### ELECTRONICS SYSTEM DESIGN

### **SECTION-4**

## <u>MULTI INPUT SYSTEM</u> CONTROLLER DESIGN AND <u>PLDs</u>

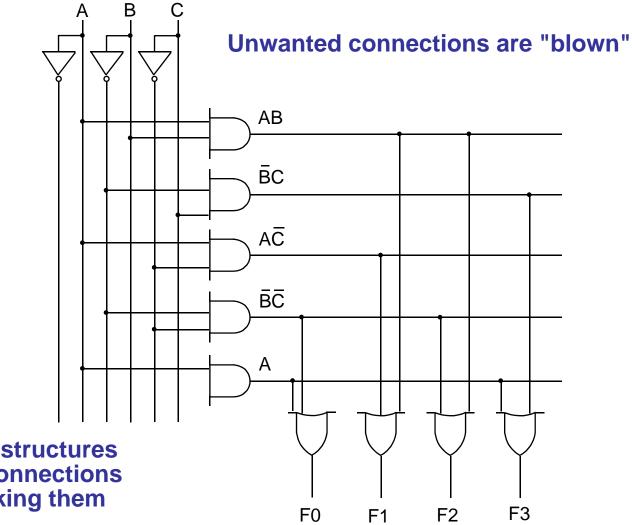

### Prgrammable Logic Organization

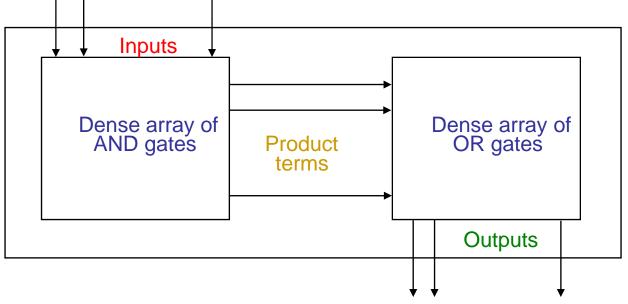

- Pre-fabricated building block of many AND/OR gates (or NOR, NAND)

- "Personalized" by making or breaking connections among the gates

Programmable Array Block Diagram for Sum of Products Form

### Basic Programmable Logic Organizations

Depending on which of the AND/OR logic arrays is programmable, we have three basic organizations

| ORGANIZATION | AND ARRAY | <b>OR ARRAY</b> |

|--------------|-----------|-----------------|

| PAL          | PROG.     | FIXED           |

| PROM         | FIXED     | PROG.           |

| PLA          | PROG.     | PROG.           |

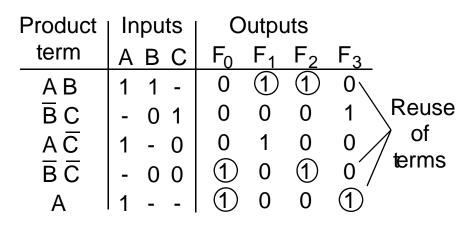

#### Key to Success: Shared Product Terms

#### **Equations**

| Example |

|---------|

|---------|

$F0 = A \pm \overrightarrow{BC}$  F1 = AC + AB  $F2 = \overrightarrow{BC} + AB$  $F3 = \overrightarrow{BC} + A$

### **Personality Matrix**

#### Input Side:

- 1 = asserted in term

- 0 = negated in term

- = does not participate

#### **Output Side:**

- 1 = term connected to output

- 0 = no connection to output

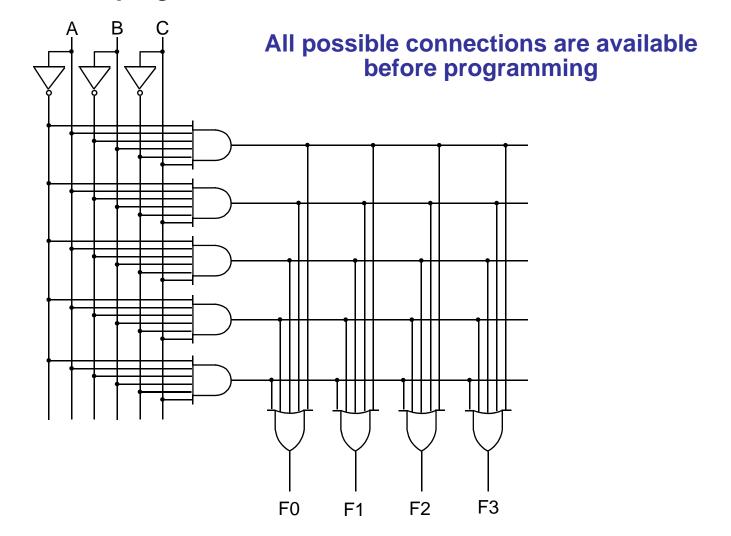

#### **Example Continued - Unprogrammed device**

Example Continued -Programmed part

Note: some array structures work by making connections rather than breaking them

AB

ĀĒ

CD

ĒD

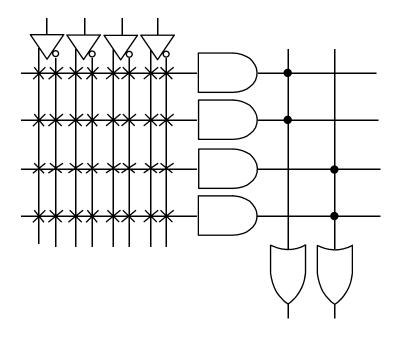

Unprogrammed device Alternative representation Short-hand notation so we don't have to draw all the wires! X at junction indicates ABCD a connection Notation for implementing  $FO = AB + \overline{A}\overline{B}$ **Programmed device**  $F1 = C\overline{D} + \overline{C}D$  $C\overline{D}+\overline{C}D$ AB+AB

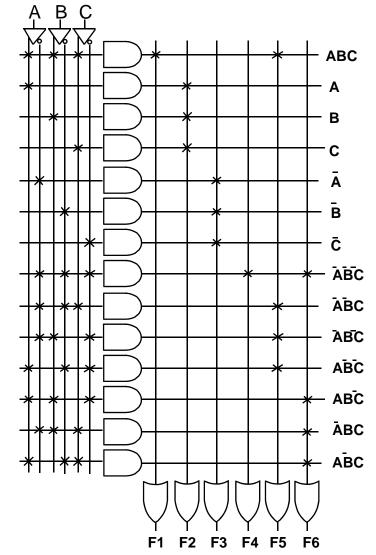

Design Example

Multiple functions of A, B, C

F1 = A B C F2 = A + B + C F3 =  $\overline{A B C}$ F4 =  $\overline{A + B + C}$ F5 = A  $\oplus$  B  $\oplus$  C F6 =  $\overline{A \oplus B \oplus C}$

### PALs and PLAs

What is difference between Programmable Array Logic (PAL) and Programmable Logic Array (PLA)?

PAL concept — implemented by Monolithic Memories AND array is programmable, OR array is fixed at fabrication

A given column of the OR array has access to only a subset of the possible product terms

**PLA concept** — Both AND and OR arrays are programmable

### PALs and PLAs

- Of the two organizations the PLA is the most flexible

- One PLA can implement a huge range of logic functions

- BUT many pins; large package, higher cost

- PALs are more restricted / you trade number of OR terms vs number of outputs

- Many device variations needed

- Each device is cheaper than a PLA

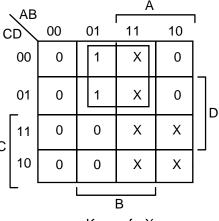

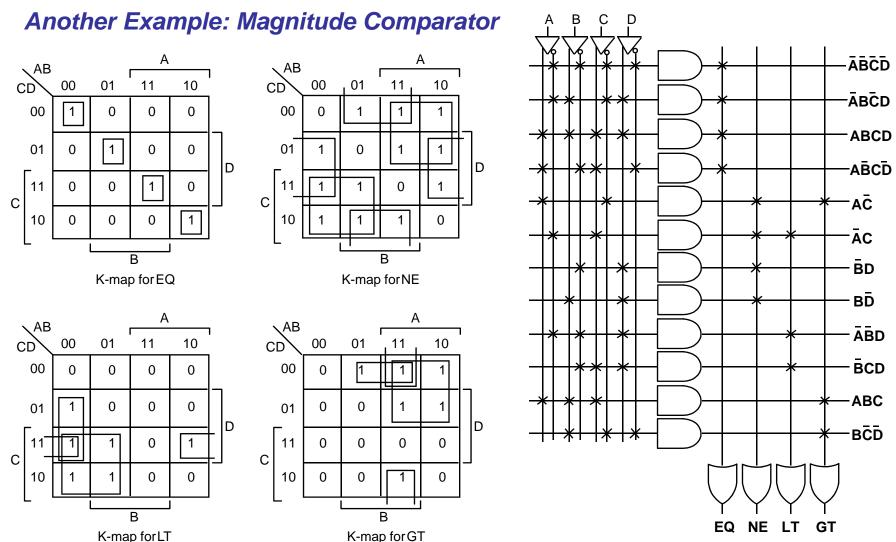

Design Example: BCD to Gray Code Converter

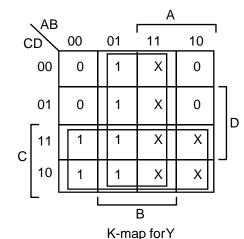

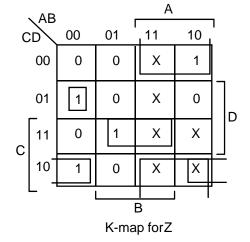

K-maps

#### **Truth Table**

| _ | А                                         | В                     | С           | D                          | W                                              | Х                     | Υ                | Ζ                               |

|---|-------------------------------------------|-----------------------|-------------|----------------------------|------------------------------------------------|-----------------------|------------------|---------------------------------|

|   | 0                                         | 0                     | 0           | 0                          | 0                                              | 0                     | 0                | 0                               |

|   |                                           | 0                     | 0           |                            | 0                                              | 0                     | 0                | 0 1 1 0 0 0 0 1 1 0 X X X X X X |

|   | 0                                         |                       | 1           | 0                          | 0<br>0                                         | 0                     | 1                | 1                               |

|   | 0<br>0<br>0<br>0                          | 0<br>0<br>1           | 1           | 1<br>0<br>1<br>0           |                                                | 0<br>0<br>1           | 1<br>1<br>1<br>1 | 0                               |

|   | 0                                         | 1                     | 0           | 0                          | 0                                              | 1                     | 1                | 0                               |

|   | 0<br>0<br>1<br>1<br>1<br>1<br>1<br>1<br>1 | 1                     | 0           | 1<br>0<br>1<br>0<br>1<br>0 | 1<br>1                                         | 1                     | 1                | 0                               |

|   | 0                                         | 1                     | 1           | 0                          | 1                                              | 0<br>0<br>0<br>X<br>X | 1                | 0                               |

|   | 0                                         | 1                     | 1           | 1                          | 1                                              | 0                     | 1                | 1                               |

|   | 1                                         | 0<br>0<br>0<br>0<br>1 | 0           | 0                          | 1<br>1<br>X<br>X<br>X<br>X<br>X<br>X<br>X<br>X | 0                     | 0                | 1                               |

|   | 1                                         | 0                     | 0<br>1<br>1 | 1                          | 1                                              | 0                     | 0<br>X           | 0                               |

|   | 1                                         | 0                     | 1           | 0                          | Х                                              | Х                     |                  | Х                               |

|   | 1                                         | 0                     | 1           |                            | Х                                              | Х                     | Х                | Х                               |

|   | 1                                         |                       | 0           | 0                          | Х                                              | Х                     | Х                | Х                               |

|   | 1                                         | 1                     | 0           | 1                          | Х                                              | Х                     | Х                | Х                               |

|   | 1                                         | 1                     | 1           | 0                          | Х                                              | Х                     | Х                | Х                               |

|   | 1                                         | 1                     | 1           | 1                          | Х                                              | Х                     | Х                | Х                               |

#### ∖AB 00 01 11 10 CD X 0 00 0 01 0 1 Х 1 D 11 0 Х Х С С 10 Х 0 В K-map forW

А

K-map forX

#### **Minimized Functions:**

$W = A \pm B D + B C$  X = B C  $Y = B \pm C$ Z = A B C D + B C D + A D + B C D

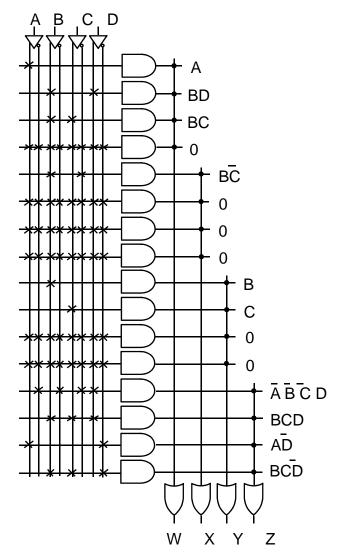

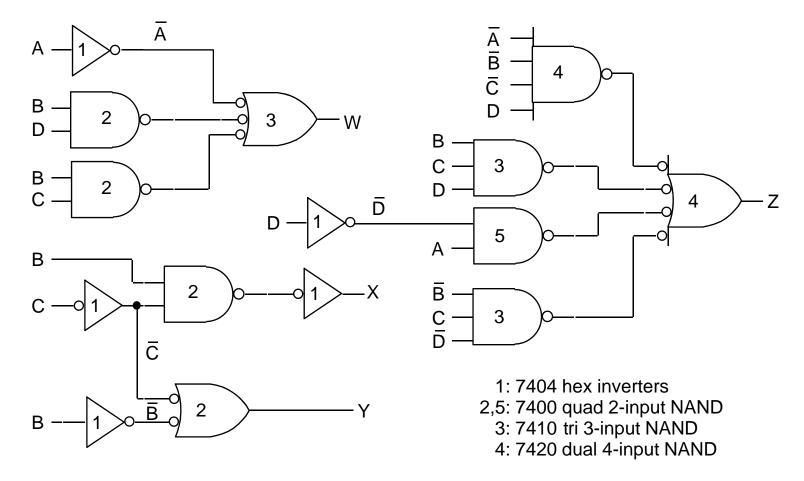

**Programmed PAL:**

#### **Minimized Functions:**

4 product terms per each OR gate

#### **Code Converter Discrete Gate Implementation**

4 SSI Packages vs. 1 PLA/PAL Package!

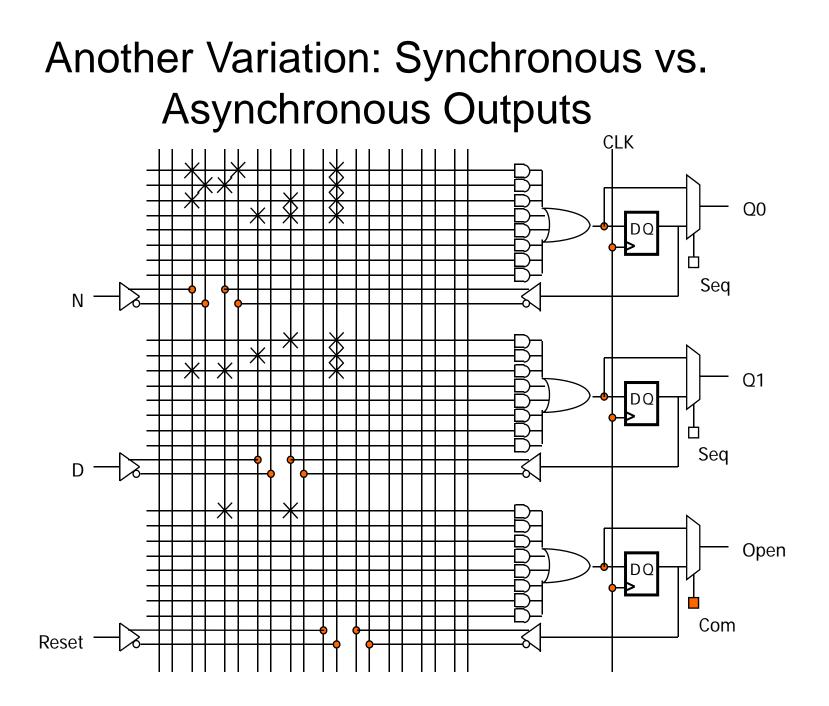

### Complex Programmable Logic Devices

- Complex PLDs typically combine PAL combinational logic with FFs

- Organized into logic blocks

- Fixed OR array size

- Combinational or registered output

- Some pins are inputs only

- Usually enough logic for simple counters, state machines, decoders, etc.

- e.g. GAL22V10, GAL16V8, etc.

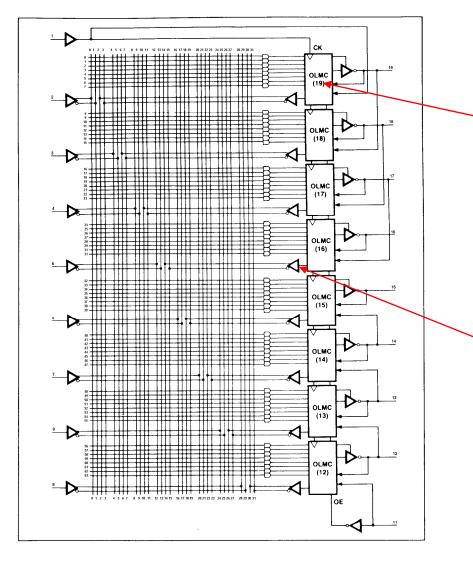

### GAL CPLD

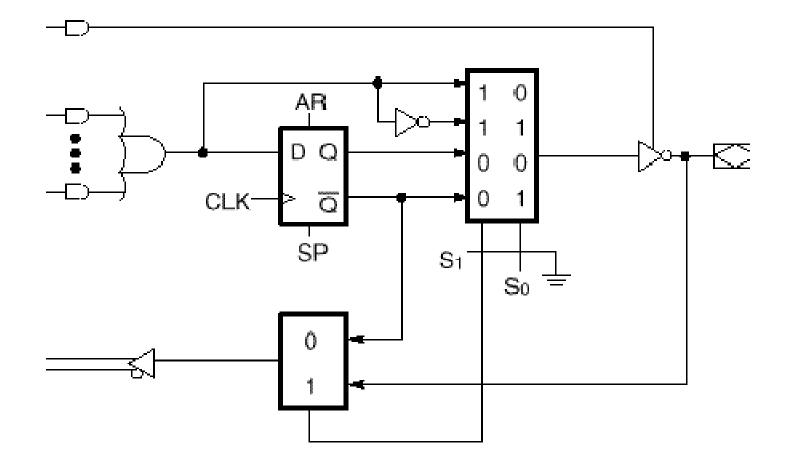

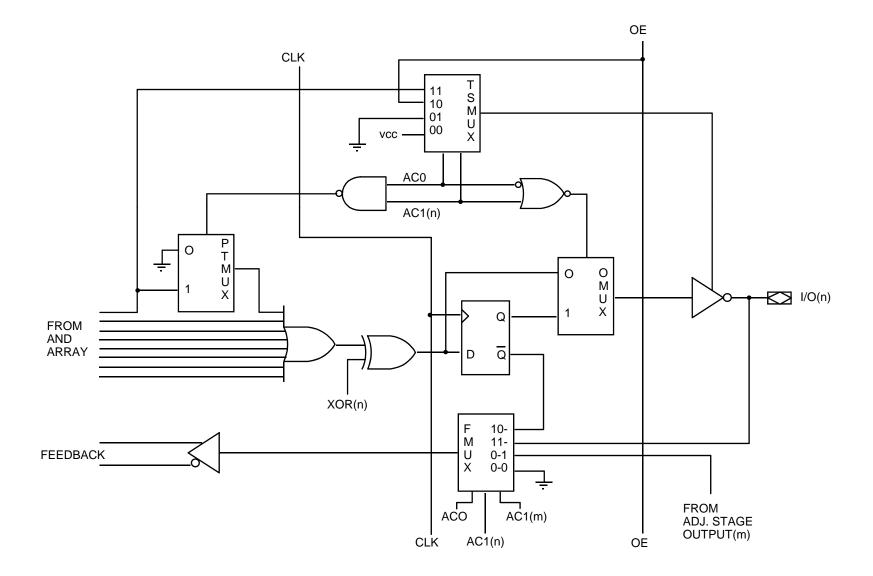

- OLMC (Output Logic MacroCell) has OR, FF, output multiplexer and I/O control logic.

Note that OLMC output is fed back to input matrix for use in other OLMCs.

### GAL22V10 OLMC Structure

### PAL22V10 OLMC Configuration Modes

- Registered Mode: active (low, high): Q' is feedback as input only, no dedicated input in this mode

- Combinational Mode: active (low, high) can feedback comb. Output (high, low) and/or dedicated input

### GAL16V8 OLMC Structure

### PAL16V8 OLMC Configuration Modes

Simple mode (combinational output)

combinational output

combinational output with feedback

dedicated input

Complex mode

combinational output, with feedback combinational input from another OLMC Registered mode: active (low, high): Q' is feedback as input (no dedicated input)

### Field Programmable Gate Arrays (FPGAs)

- FPGAs have much more logic than CPLDs

- 2K to >10M equivalent gates

- Requires different architecture

- FPGAs can be RAM-based or Flash-based

- RAM FPGAs must be programmed at power-on

- External memory needed for programming data

- May be dynamically reconfigured

- Flash FPGAs store program data in non-volatile memory

- Reprogramming is more difficult

- Holds configuration when power is off

# • Typical organization in 2-D array

- Configurable logic blocks (CLBs) contain functional logic (could be similar to PAL22V10)

- Combinational functions plus FFs

- Complexity varies by device

- CLB interconnect is either local or long line

- CLBs have connections to local neighbors

- Horizontal and vertical channels use for long distance

- Channel intersections have switch matrix

- IOBs (I/O logic Blocks) connect to pins

- Usually have some additional C.L./FF in block

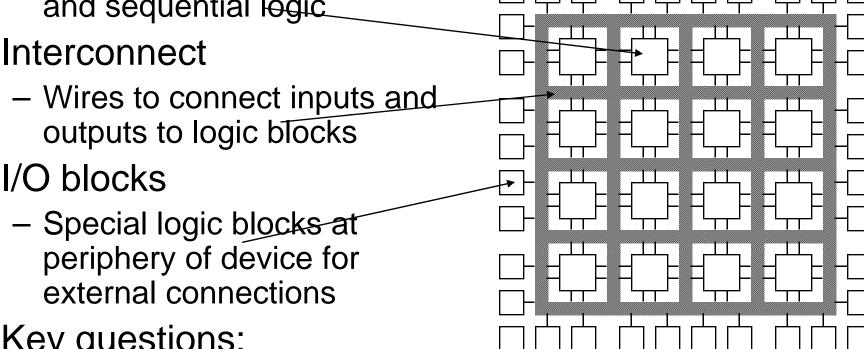

### Field-Programmable Gate Arrays structure

- Logic blocks

- To implement combinational and sequential logic

- Interconnect

- I/O blocks

- Key questions:

- How to make logic blocks programmable?

- How to connect the wires?

- After the chip has been fabbed

- HW problems: 7-19, 7-20, 7-22, 7-23, 7-26 due 22/9/07